# Embedded Xinu on the ARM 32F4 Discovery Board

By: Ethan Weber

Department: Mathematics, Statistics, and Computer Science

Mentor: Dr. Dennis Brylow

### Introduction

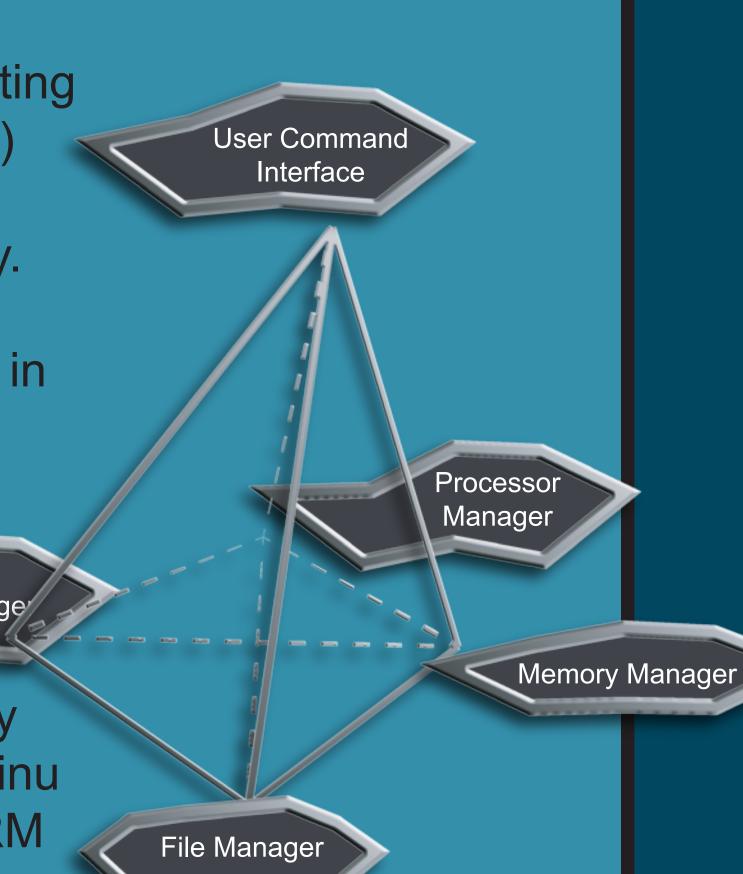

Embedded Xinu is a small operating system (modeled in this diagram) that is used for educational purposes at Marquette University. In order to port Xinu to the ARM architecture, each of the corners in the pyramid must be supported. The three focused on in this research project include the User Device Manage Command Interface, Processor Manager, and Memory Manager. Once implemented, Xinu will be able to function on the ARM 32F4 Discovery board, thus increasing the educational experience offered by Xinu.

#### Motivation

- Expand the Embedded Xinu Universe

- Support Audio Input and Output on Xinu

- Support Motion Detection on Xinu

- Further Enrich the Xinu Educational Experience

- Spark Increased Interest in Embedded Xinu

## ARM 32F4 Discovery

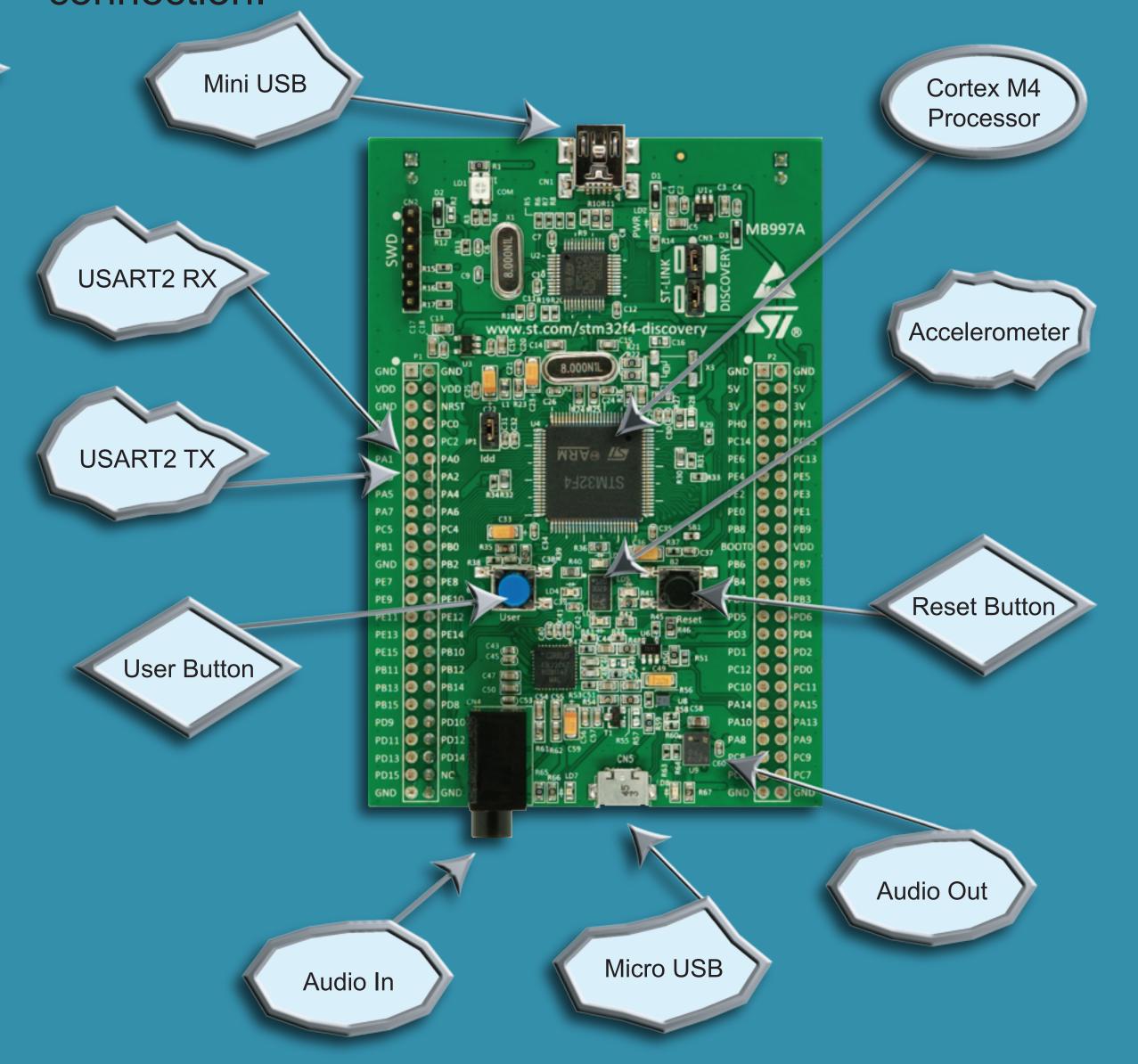

The ARM 32F4 Discovery board is host to an M4 Cortex processor. This processor runs on THUMB assembly code. The instruction set for the M4 is a super set to all other M series processors. This means that assembly programs written for any of the ARM M series processors will run on this board. Below there is a diagram showing the main components that make up the ARM Discovery board. The USART2 RX and TX labels point towards two pins that were used to create a serial connection.

### References

- "Course Announcement." MU COEN 4820 Operating Systems and Networks. N.p., n.d.

- Web. 26 June 2012. <a href="http://www.eng.mu.edu/corlissg/OpSys.12Sp/">http://www.eng.mu.edu/corlissg/OpSys.12Sp/</a>. [Flynn, Ida M., and Ann McIver McHoes. Understanding Operating Systems. Boston, MA:

- Thomson Course Technology, 2006. Print.

"Main Page." Embedded Xinu. N.p., n.d. Web. 26 June 2012.

<a href="http://xinu.mscs.mu.edu/Main\_Page">http://xinu.mscs.mu.edu/Main\_Page</a>.

- Noergaard, Tammy. Embedded Systems Architecture: A Comprehensive Guide for

- Engineers and Programmers. Amsterdam: Elsevier/Newnes, 2005. Print.

"STM32F4DISCOVERY." STMicroelectronics. N.p., n.d. Web. 26 June 2012.

<a href="http://www.st.com/internet/evalboard/product/252419.jsp">http://www.st.com/internet/evalboard/product/252419.jsp</a>.

#### ARM vs MIPS

| ARM      |       |

|----------|-------|

| Register | Alias |

| 0-3:     | a1-a4 |

| 4-11:    | v1-v8 |

| 12:      | IP    |

| 13:      | SP    |

| 14:      | LR    |

| 15:      | PC    |

| 16:      | CPSR  |

Above are representations of the processor registers needed to perform a context switch. The main differences to consider with ARM include the lack of callee save registers. For ARM, only

| MIPS       |       |  |

|------------|-------|--|

| Register   | Alias |  |

| 0:         | zero  |  |

| 1:         | AT    |  |

| 2-3:       | v0-v1 |  |

| 4-7:       | a0-a1 |  |

| 8-15:      | t0-t7 |  |

| 16-23:     | s0-s7 |  |

| 24-25:     | t8-t9 |  |

| 26-27:     | k0-k1 |  |

| 28:        | s8    |  |

| 29:        | sp    |  |

| 29:<br>30: | s9    |  |

| 31:        | ra    |  |

the special purpose registers (capital letters) and the arguments (a1-a4) must be saved by the context switch. However, ARM also has more special registers than MIPS.

### Progress/Future Work

Built Serial Connection

- Adapted USART Code to Communicate over Serial Connection

- Created Code for a Context Switch

Future Work

- Create Interrupts and Scheduling

- Support the Audio I/0 and Accelerometer

- Create Relative Coursework for a Classroom Environment