### Introduction

The Embedded Xinu project is being conducted by both graduate and undergraduate students in the Systems Laboratory in the Math, Statistics, and Computer Science department of Marquette University in Milwaukee, Wisconsin [1]. The existing system, which is being used for Operating Systems, Hardware Systems, Embedded Systems and Networks courses offered at Marquette University, uses a pool of Linksys WRT54GL routers to run custom student made Xinu kernel images. The reason why we chose to convert the existing system from a pool of Linksys WRT54GL routers to a pool of Raspberry Pi's was because Raspberry Pis are:

- 15 dollars cheaper than the routers

- more open than the routers

- more modern than the routers

- smaller than the routers

Figure 1: A picture of a Raspberry Pi model B.

## **MIPS Vs. ARM Architecture**

The Linksys WRT54GL routers use MIPS architecture processors compared to the Raspberry Pi, which uses ARM architecture processors. Biggers (2013)[3] already ported the Xinu operating system for the Raspberry Pis, so they rewrote the supporting Xinu kernel MIPS assembly code to ARM assembly. Unfortunately, the courses at Marquette, which used the Embedded Xinu project, has all of its assignments, tests and quizzes use MIPS assembly language. Therefore, we had to convert the MIPS assembly assignments to ARM assembly to ensure this was viable for the fall 2015 semester. As figure 2 shows, MIPS does have more general purpose registers than ARM. However, we found that the students benefit greatly from the switch from MIPS assembly to ARM assemily in that they can reduce their code for a lot of assignments, such as context switching processes. Additionally, students benefit from

# A pool of Raspberry Pi's running Xinu for college computer science curriculum

Jason Arnold, Casey O'hare, Omokolade Hunpatin, Luke Mivshek Marquette University, Wisconsin

using Arm assembly in that when specifying a stack pointer offset to load or store operation, one can use a register in ARM. This allows a student to write assembly programs a lot easier.

MIPS general purpose registers

| Register<br>Name    | "regdef.h" Naming<br>Convention | Possible Usages                  | Register | Usage                            |

|---------------------|---------------------------------|----------------------------------|----------|----------------------------------|

| \$0                 | zero                            | wired to zero value              | Name     | a subc                           |

| \$1                 | \$at                            | reserved for the assembler       |          |                                  |

| \$2                 | \$v0                            | return values                    | RO       | general purpose (scratch)        |

| \$3                 | \$v1                            |                                  |          |                                  |

| \$4                 | \$a0                            | arguments                        | R1       |                                  |

| \$5                 | \$ <mark>a</mark> 1             |                                  |          |                                  |

| \$6                 | \$ <mark>a</mark> 2             |                                  | R2       |                                  |

| \$7                 | \$a3                            |                                  | 02       |                                  |

| \$8                 | \$t0                            | temporary                        | R3       |                                  |

| \$9                 | \$t1                            |                                  | R4       | general purpose                  |

| \$ <b>1</b> 0       | \$t2                            |                                  | N4       |                                  |

| \$ <mark>1</mark> 1 | \$t3                            |                                  | R5       |                                  |

| \$ <mark>1</mark> 2 | \$t4                            |                                  | 10       |                                  |

| \$ <mark>1</mark> 3 | \$t5                            |                                  | R6       |                                  |

| \$ <mark>1</mark> 4 | \$t6                            |                                  |          |                                  |

| \$ <b>1</b> 5       | \$t7                            |                                  | R7       |                                  |

| \$ <b>1</b> 6       | \$s0                            | saved                            |          |                                  |

| \$ <b>1</b> 7       | \$s1                            |                                  | R8       |                                  |

| \$ <b>1</b> 8       | \$s2                            |                                  | 00       |                                  |

| \$ <b>1</b> 9       | \$s3                            |                                  | R9       |                                  |

| \$ <mark>2</mark> 0 | \$s4                            |                                  | D10      |                                  |

| \$ <mark>2</mark> 1 | \$s5                            |                                  | R10      |                                  |

| \$ <mark>2</mark> 2 | \$s6                            |                                  | D11      |                                  |

| \$ <b>2</b> 3       | \$s7                            |                                  | R11      |                                  |

| \$ <mark>2</mark> 4 | \$t8                            | temporary                        | R12      |                                  |

| \$ <b>2</b> 5       | \$t9                            |                                  | 1112     |                                  |

| \$ <mark>2</mark> 6 | \$k0                            | reserved for the OS kernel       | R13      | reserved for the stack pointer   |

| \$ <mark>2</mark> 7 | \$k1                            |                                  | 1140     |                                  |

| \$ <mark>2</mark> 8 | \$gp                            | reserved for the global pointer  | R14      | linker register                  |

| \$29                | \$sp                            | reserved for the stack pointer   |          |                                  |

| \$ <mark>3</mark> 0 | \$s8, \$fp                      | saved, frame pointer             | R15      | reserved for the program counter |

| \$31                | \$ra                            | linker register (return address) |          |                                  |

Figure 2: MIPS Architecture general purpose registers and ARM Architecture general purpose registers side by side

MIPS vs. ARM Assembly[4]

### Mailbox property interface

When we first started trying to set up the pool of Raspberry Pi's, we initially wanted to test communicating with the Raspberry Pi's over the network. We found that the port of Xinu for the Raspberry Pi couldn't find the hardware MAC address for the Raspberry Pi and would generate a random hardware MAC address every time the Raspberry Pi booted up. This was a problem because to communicate with a Raspberry Pi over the network, it needs a static hardware MAC address that needs to be known in order for us to designate it an IP address.

A pool of Raspberry Pi's running Xinu for college computer science curriculum

#### ARM general purpose registers

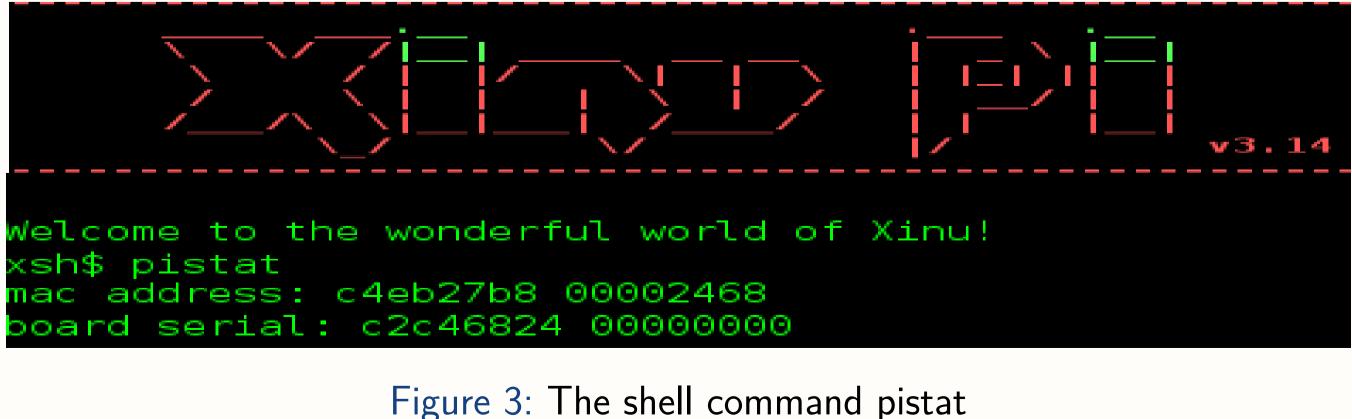

We found out about the Mailbox property interface, which is the primary means of communication between the ARM and the VideoCore firmware running on the GPU [5]. Using the mailbox property interface we created a Xinu shell command called pistat that reads a Raspberry Pi's hardware information. Additionally, we created functions that takes a parameter of what hardware information a user wants then returns that hardware information. The general procedure to read from a mailbox:

Read the status register until the empty flag is not set

**2** Read data from the read register from 1

The upper 28 bits are the returned data [6]

#### Acknowledgments

The students on the building a pool of XinuPi's team were supported by the National Science Foundation, grants CNS-1339392, and ACI 1461264. The porting of the Xinu Operating system from the Linksys Routers to the Raspberry Pi and the shell command that allows one to receive a kernel's binary through tftp and boot itself using that kernel's binary in RAM is thanks to Eric Biggers, Tyler Much, and Farzeen Harunani [3].

- [1] http://xinu.mscs.mu.edu/Main\_Page

- [2] https://www.raspberrypi.org/help/what-is-a-raspberry-pi

- Education. 2013.

- MIPSvsARM.pdf

- [5] https://github.com/raspberrypi/firmware/wiki

#### Solution:

- 3 If the lower four bits do not match the channel number desired then repeat

### References

[3] Biggers, Eric, et al. "XinuPi: Porting a Lightweight Educational Operating System to the Raspberry Pi." 2013 Proceedings of the Workshop on Embedded and Cyber-Physical Systems

[4] http://www.ece.gatech.edu/academic/courses/ece2035/readings/embedded/

[6] https://github.com/raspberrypi/firmware/wiki/Accessing-mailboxes

[7] https://www.raspberrypi.org/blog/price-cut-raspberry-pi-model-b-now-only-25/